Urządzenia cyfrowe: przerzutniki, komparatory i rejestry

Urządzenia cyfrowe zbudowane są na elementach logicznych, dlatego podlegają prawom algebry logicznej. Podstawowymi urządzeniami technologii cyfrowej, obok urządzeń logicznych, są przerzutniki.

Urządzenia cyfrowe zbudowane są na elementach logicznych, dlatego podlegają prawom algebry logicznej. Podstawowymi urządzeniami technologii cyfrowej, obok urządzeń logicznych, są przerzutniki.

Wyzwalacz (Angielski wyzwalacz - wyzwalacz) - urządzenie elektroniczne, które ma dwa stabilne stany i może przeskakiwać z jednego stanu do drugiego pod wpływem zewnętrznego impulsu.

Wyzwalacze, a dokładniej układy wyzwalające, nazywane są dużą klasą urządzeń elektronicznych, które mają zdolność pozostawania przez długi czas w jednym z dwóch stabilnych stanów i naprzemiennego ich działania pod wpływem sygnałów zewnętrznych. Każdy warunek wyzwalania można łatwo rozpoznać po wartości napięcia wyjściowego.

Każdy stan wyzwalania odpowiada określonemu (wysokiemu lub niskiemu) poziomowi napięcia wyjściowego:

1) wyzwalacz jest ustawiony na jeden stan — poziom «1».

2) przerzutnik jest resetowany — stan „0” na wyjściu.

Stan ustalony pozostaje tak długo, jak jest to pożądane i może być zmieniony za pomocą impulsu zewnętrznego lub poprzez wyłączenie napięcia zasilającego. Che.przerzutnik to elementarny element pamięci zdolny do przechowywania najmniejszej jednostki informacji (jeden bit) „0” lub „1”.

Przerzutniki mogą być zbudowane na elementach dyskretnych, elementach logicznych, na układzie scalonym lub stanowią część układu scalonego.

Główne typy przerzutników to: płetwy RS-, D-, T- i JK... Ponadto przerzutniki dzielą się na asynchroniczne i synchroniczne. W uruchamianiu asynchronicznym przełączanie z jednego stanu do drugiego odbywa się bezpośrednio po dotarciu sygnału do wejścia informacyjnego. Oprócz wejść danych, przerzutniki zsynchronizowane posiadają wejście zegarowe. Ich przełączanie odbywa się tylko w obecności zezwalającego impulsu zegarowego.

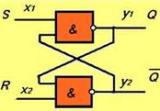

Wyzwalacz RS ma co najmniej dwa wejścia: S (set — set) — wyzwalacz jest ustawiany w stan poziomu „1” i R (reset) — wyzwalacz jest resetowany do stanu poziomu „0”. (Rys. 1).

W obecności wejścia C przerzutnik jest synchroniczny — przełączenie przerzutnika (zmiana stanu wyjścia) może nastąpić dopiero w momencie nadejścia impulsu synchronizującego (synchronizującego) na wejście C.

Rysunek 1 — Konwencjonalne graficzne przedstawienie przerzutnika RS i cel wniosków a) asynchroniczny, b) synchroniczny

Oprócz wyjścia bezpośredniego przerzutnik może mieć również wyjście odwrotne, którego sygnał będzie przeciwny.

W tabeli 1 przedstawiono stany, jakie może przyjmować przerzutnik podczas pracy. W tabeli przedstawiono wartości sygnałów wejściowych S i R w określonej chwili czasu tn oraz stan przerzutnika (wyjścia bezpośredniego) w następnej chwili czasu tn + 1 po nadejściu następnego rośliny strączkowe. Na nowy stan wyzwalania ma również wpływ poprzedni stan Qn.

Che.jeśli konieczne jest wpisanie na wyzwalacz „1” — podajemy impuls na wejście S, jeśli „0” — wysyłamy impuls na wejście R.

Kombinacja S = 1, R = 1 jest kombinacją zabronioną, ponieważ nie można przewidzieć, jaki stan zostanie ustalony na wyjściu.

Tabela 1 - Tabela stanu synchronicznego przerzutnika RS

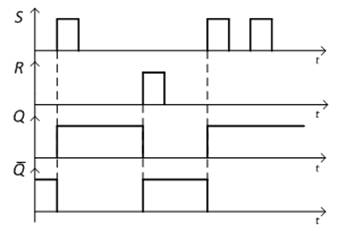

Działanie przerzutnika można również zobaczyć za pomocą wykresów czasowych (rys. 2).

Rysunek 2 — Diagramy czasowe asynchronicznego przerzutnika RS

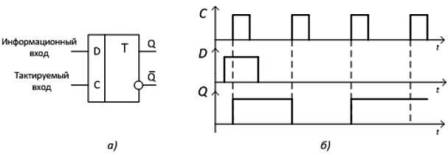

D-trigger (z angielskiego delay — delay) ma jedno wejście informacyjne i wejście zegarowe (synchronizujące) (ryc. 3).

Przerzutnik D przechowuje i przechowuje na wyjściu Q sygnał, który był na wejściu danych D w momencie nadejścia impulsu zegarowego C. Przerzutnik przechowuje informację zapisaną, gdy C = 1.

Tabela 2-Tabela stanów przerzutnika D

Rysunek 3 — Wyzwalacz D: a) konwencjonalna reprezentacja graficzna, b) schematy czasowe działania

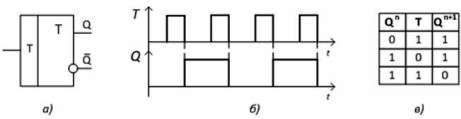

Wyzwalacze T (z angielskiego tumble — przewracanie, salto), zwane też przerzutnikami liczącymi, mają jedno wejście informacyjne T. Każdy impuls (zanik impulsu) wejścia T (wejście zliczające) przełącza wyzwalacz w stan przeciwny.

Rysunek 4 przedstawia symbolikę wyzwalacza T (a) i schematy czasowe działania (b).

Rysunek 4-T-flip-flop a) notacja konwencjonalno-graficzna, b) diagramy czasowe działania c) tablica stanów

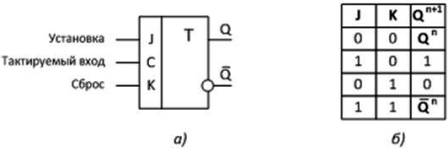

Wyzwalacz JK (z angielskiego jump — jump, keer — hold) ma dwa wejścia danych J i K oraz wejście zegarowe C. Przypisanie pinów J i K jest podobne do przypisania pinów R i S, ale wyzwalacz ma żadnych zabronionych kombinacji. Jeśli J = K = 1, zmienia swój stan na przeciwny (rys. 5).

Przy odpowiednim podłączeniu wejść, wyzwalacz może pełnić funkcje wyzwalaczy RS-, D-, T, tj. jest uniwersalnym wyzwalaczem.

Rysunek 5 -JK -flip-flop a) notacja konwencjonalna -graficzna, b) skrócona tablica stanów

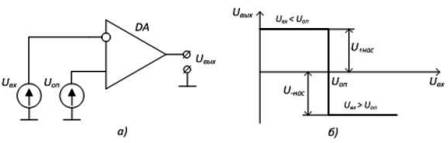

Komparator (porównaj — porównaj) — urządzenie porównujące dwa napięcia — wejście Uin z odniesieniem Uref. Napięcie odniesienia jest napięciem stałym z polaryzacją dodatnią lub ujemną, napięcie wejściowe zmienia się w czasie. Najprostszy obwód komparatora oparty na wzmacniaczu operacyjnym pokazano na rysunku 6, a. Jeśli Uin Uop na wyjściu U — nas (ryc. 6, b).

Rysunek 6 — Komparator wzmacniacza operacyjnego: a) najprostszy schemat b) charakterystyka działania

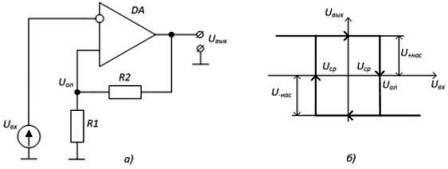

Komparator z dodatnim sprzężeniem zwrotnym nazywany jest wyzwalaczem Schmitta. Jeśli komparator przełącza się z „1” na „0” i odwrotnie przy tym samym napięciu, wówczas wyzwalacz Schmitta - przy różnych napięciach. Napięcie odniesienia tworzy obwód PIC R1R2, sygnał wejściowy jest podawany na wejście odwracające wzmacniacza operacyjnego. Rysunek 7, b przedstawia charakterystykę przenoszenia wyzwalacza Schmitta.

Przy ujemnym napięciu na wejściu inwentaryzacyjnym systemu operacyjnego Uout = U + sat. Oznacza to, że na wejście nieodwracające działa dodatnie napięcie. Wraz ze wzrostem napięcia wejściowego prąd Uin > Uneinv. (Uav — trigger) komparator przechodzi do stanu Uout = U -sat. Napięcie ujemne jest przykładane do wejścia nieodwracającego. Odpowiednio, przy spadku napięcia wejściowego w chwili Uin <Uneinv. (Uav — trigger) komparator przechodzi w stan Uout = U + sat.

Rysunek 7 — Operacja Schmitta wzmacniacza operacyjnego: a) najprostszy schemat b) charakterystyka działania

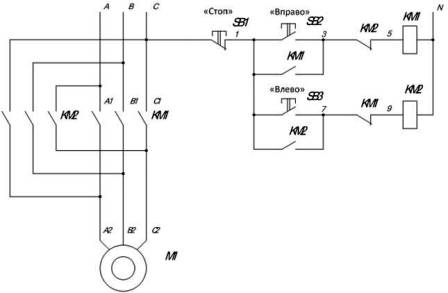

Przykład. Rysunek 8 przedstawia schemat przekaźnika-stycznika do sterowania silnikiem elektrycznym, umożliwiającego jego uruchamianie, zatrzymywanie i bieg wsteczny.

Rysunek 8 — Schemat sterowania silnikiem ze stycznikiem przekaźnikowym

Komutacja silnika elektrycznego odbywa się za pomocą rozruszników magnetycznych KM1, KM2. Swobodnie zwarte styki KM1, KM2 uniemożliwiają jednoczesną pracę rozruszników magnetycznych. Swobodnie otwarte styki KM1, KM2 zapewniają samoblokowanie przycisków SB2 i SB3.

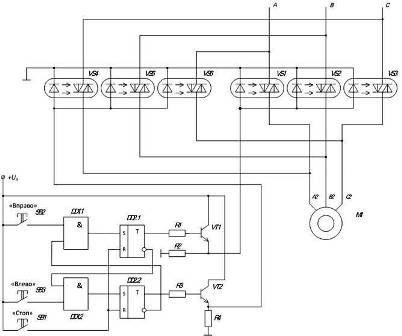

Aby poprawić niezawodność działania, konieczna jest wymiana obwodów sterujących przekaźnika-stycznika i obwodów mocy na układ bezdotykowy z wykorzystaniem urządzeń i urządzeń półprzewodnikowych.

Rysunek 9 przedstawia bezdotykowy obwód sterowania silnikiem.

Styki mocy rozruszników magnetycznych zostały zastąpione opto-symistorami: KM1-VS1-VS3, KM2-VS4-VS6. Zastosowanie optozymistorów umożliwia odizolowanie niskoprądowego obwodu sterującego od obwodu zasilającego o dużej mocy.

Spusty zapewniają samoblokujące przyciski SB2, SB3. Elementy logiczne ORAZ zapewniają jednoczesną aktywację tylko jednego z rozruszników magnetycznych.

Gdy tranzystor VT1 się otwiera, prąd przepływa przez diody LED pierwszej grupy opto-symistorów VS1-VS3, zapewniając w ten sposób przepływ prądu przez uzwojenia silnika.Otwarcie tranzystora VT2 zasila drugą grupę opto-symistorów VS4 -VS6, zapewniający obrót silnika elektrycznego w przeciwnym kierunku.

Rysunek 9 — Bezdotykowy obwód sterowania silnikiem

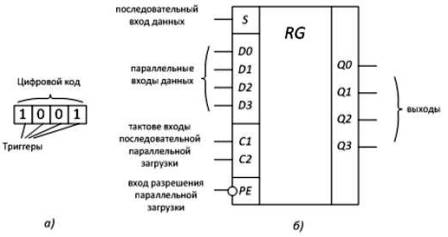

Rejestr – urządzenie elektroniczne przeznaczone do krótkotrwałego przechowywania i konwersji wielocyfrowych liczb binarnych. Rejestr składa się z przerzutników, których liczba określa, ile bitów liczby binarnej może przechowywać rejestr - rozmiar rejestru (ryc. 10, a). Elementy logiczne mogą służyć do organizowania działania wyzwalaczy.

Rysunek 10 — Rejestr: a) przedstawienie ogólne, b) konwencjonalna notacja graficzna

Zgodnie z metodą wprowadzania i wyprowadzania informacji rejestry dzielą się na równoległe i szeregowe.

W rejestrze sekwencyjnym przerzutniki są połączone szeregowo, to znaczy wyjścia poprzedniego przerzutnika przekazują informacje do wejść następnego przerzutnika. Wejścia zegara przerzutnika C są połączone równolegle. Rejestr taki posiada jedno wejście danych oraz wejście sterujące – wejście zegarowe C.

Rejestr równoległy zapisuje jednocześnie do przerzutników, dla których dostępne są cztery wejścia danych.

Rysunek 10 przedstawia UGO i przydział pinów czterobitowego rejestru szeregowego równoległego.