Magistrala I2C — przypisanie, urządzenie, transfer danych, adresowanie

Podczas tworzenia obwodu elektronicznego wielu programistów staje przed koniecznością użycia dużej liczby pośrednich układów scalonych do dopasowywania, próbkowania i adresowania jego poszczególnych bloków. Aby zminimalizować liczbę dodatkowych układów scalonych, firma Philips już w latach 80.

Dziś sam Philips produkuje ponad sto urządzeń kompatybilnych z I2C dla sprzętu elektronicznego o szerokim zastosowaniu: pamięci, systemy procesorów wideo, przetworniki analogowo-cyfrowe i cyfrowo-analogowe, sterowniki wyświetlaczy itp.

Magistrala I2C jest modyfikacją szeregowego protokołu wymiany danych zdolną do przesyłania 8-bitowych danych szeregowych w zwykłym „szybkim” trybie z szybkością od 100 do 400 kb/s. Proces wymiany danych realizowany jest tutaj tylko dwoma przewodami (nie licząc przewodu wspólnego): linią SDA do transmisji danych oraz linią SCL do synchronizacji.

Magistrala staje się dwukierunkowa dzięki temu, że kaskady wyjść urządzeń podłączonych do magistrali posiadają otwarte kolektory lub kanały, replikując w ten sposób okablowanie AND. W rezultacie magistrala minimalizuje liczbę połączeń między układami scalonymi, pozostawiając mniej wymaganych pinów i ścieżek na płytce. W rezultacie sama płytka okazuje się prostsza, bardziej zwarta i bardziej zaawansowana technologicznie w produkcji.

Protokół ten umożliwia wyłączenie dekoderów adresów i innej zewnętrznej logiki negocjacji. Liczba chipów, które mogą działać jednocześnie na szynie I2C, jest ograniczona jej pojemnością — maksymalnie 400 pF.

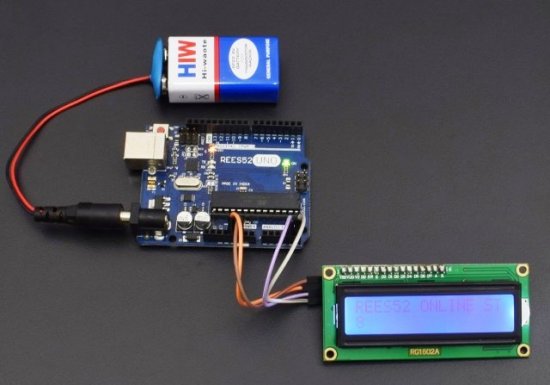

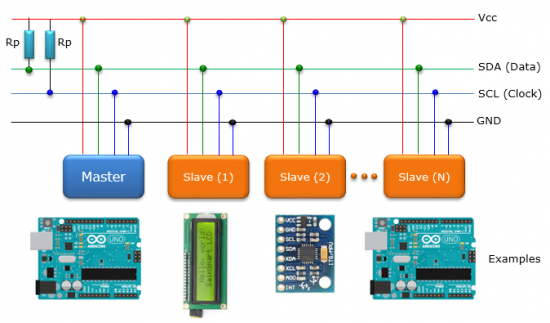

Układy scalone zgodne z I2C mają sprzętowy algorytm tłumienia szumów, aby zapewnić integralność danych nawet w obecności silnych zakłóceń. Takie urządzenia mają interfejs, który pozwala mikroukładom komunikować się ze sobą nawet wtedy, gdy ich napięcia zasilania są różne. Na poniższym rysunku możesz zapoznać się z zasadą łączenia kilku mikroukładów przez wspólną magistralę.

Każde z urządzeń podłączonych do magistrali ma swój unikalny adres, jest przez niego określany i zgodnie z przeznaczeniem urządzenia może pracować jako odbiornik lub jako nadajnik. Podczas transmisji danych urządzenia te mogą być nadrzędne (master) lub podrzędne (slave). Master to urządzenie inicjujące transmisję danych i generujące sygnały zegarowe na linii SCL. Urządzenie podrzędne w stosunku do urządzenia nadrzędnego jest urządzeniem docelowym.

W danym momencie pracy na magistrali I2C tylko jedno urządzenie może pełnić rolę mastera; generuje sygnał na linii SCL.Urządzenie nadrzędne może być odbiornikiem nadrzędnym lub nadrzędnym nadajnikiem.

W zasadzie magistrala dopuszcza kilka różnych masterów, ale nakłada ograniczenia na charakterystykę formowania sygnałów sterujących i monitorowania stanu magistrali; oznacza to, że kilka masterów może rozpocząć nadawanie w tym samym czasie, ale konflikty tego typu są eliminowane dzięki arbitrażowi, czyli zachowaniu mastera, gdy wykryje, że magistrala jest zajęta przez innego mastera.

Synchronizację pary urządzeń zapewnia fakt, że wszystkie urządzenia są podłączone do magistrali, tworząc okablowanie „AND”. Początkowo sygnały SDA i SCL są wysokie.

START i STOP

Wymiana rozpoczyna się od wygenerowania przez mastera stanu „START”: na linii SDA sygnał przechodzi ze stanu wysokiego na niski, podczas gdy na linii SCL utrzymuje się stabilny wysoki poziom. Wszystkie urządzenia podłączone do magistrali odbierają tę sytuację jako polecenie rozpoczęcia wymiany.

Każdy master generuje indywidualny sygnał zegarowy na linii SCL podczas transmisji danych na magistrali.

Wymiana kończy się utworzeniem przez mastera stanu STOP: na linii SDA sygnał zmienia się z niskiego na wysoki, natomiast na linii SCL utrzymuje się stabilny wysoki poziom.

Sterownik jest zawsze źródłem sygnałów START i STOP. Gdy tylko sygnał «START» zostanie ustalony, oznacza to, że linia jest zajęta. Linia jest wolna po wykryciu sygnału STOP.

Natychmiast po zadeklarowaniu stanu START master przełącza linię SCL w stan niski i wysyła na linię SDA najbardziej znaczący bit pierwszego bajtu komunikatu. Liczba bajtów w wiadomości nie jest ograniczona.Zmiany na linii SDA są możliwe tylko wtedy, gdy poziom sygnału na linii SCL jest niski. Dane są ważne i nie należy ich zmieniać tylko wtedy, gdy impuls synchronizacji jest wysoki.

Potwierdzenie odebrania bajtu z nadajnika nadrzędnego przez odbiornik podrzędny następuje poprzez ustawienie specjalnego bitu potwierdzenia na linii SDA po odebraniu ósmego bitu danych.

POTWIERDZENIE

Tak więc wysłanie 8 bitów danych z nadajnika do odbiornika kończy się dodatkowym impulsem na linii SCL, gdy urządzenie odbierające ma niski poziom na linii SDA, co wskazuje, że odebrało cały bajt.

Potwierdzenie jest integralną częścią procesu przenoszenia danych. Master generuje impuls synchronizacji. Nadajnik wysyła stan niski do SDA, gdy zegar potwierdzający jest aktywny. Gdy impuls synchronizacji jest wysoki, odbiornik musi utrzymywać SDA na niskim poziomie.

Jeśli docelowy slave nie potwierdza swojego adresu, na przykład dlatego, że jest aktualnie zajęty, linia danych musi być utrzymywana w stanie wysokim. Kapitan może następnie dać sygnał STOP, aby przerwać wysyłkę.

Jeżeli odbiór jest realizowany przez odbiornik nadrzędny, to jest on zobowiązany do poinformowania nadajnika podrzędnego po zakończeniu transmisji – nie poprzez potwierdzenie ostatniego bajtu. Nadajnik Slave zwalnia linię danych, aby Master mógł wysłać sygnał STOP lub powtarzający się sygnał START.

Synchronizację urządzeń zapewnia fakt, że połączenia do linii SCL realizowane są na zasadzie „AND”.

Master nie ma wyłącznego prawa do kontrolowania przejścia linii SCL z niskiego na wysoki.Jeśli urządzenie podrzędne potrzebuje więcej czasu na przetworzenie odebranego bitu, może niezależnie utrzymywać SCL w stanie niskim, dopóki nie będzie gotowe do odebrania następnego bitu danych. Linia SCL w takiej sytuacji będzie niska przez czas trwania najdłuższego impulsu synchronizacji niskiego poziomu.

Urządzenia z najniższym utrzymującym się niskim poziomem pozostaną bezczynne do końca długiego okresu. Gdy wszystkie urządzenia zakończą okres niskiej synchronizacji, SCL przejdzie w stan wysoki.

Wszystkie urządzenia zaczną taktować w górę, a pierwsze urządzenie, które zakończy swój okres, jako pierwsze ustawi linię SCL na niskim poziomie. W rezultacie o czasie trwania stanu niskiego SCL będzie decydował najdłuższy stan niski impulsu synchronizacyjnego jednego z urządzeń, a o czasie trwania stanu wysokiego najkrótszy okres synchronizacji jednego z urządzenia.

Sygnały synchronizacji mogą być wykorzystywane przez odbiorniki do sterowania transmisją danych na poziomie bitowym i bajtowym.

Jeśli urządzenie jest w stanie odbierać bajty z dużą szybkością, ale zapisanie odebranego bajtu lub przygotowanie się do odbioru następnego zajmuje pewną ilość czasu, może nadal utrzymywać niski poziom SCL po odebraniu i potwierdzeniu bajtu, zmuszając nadajnik w stan czuwania.

Mikrokontroler bez wbudowanych układów sprzętowych, np. na poziomie bitowym, może spowalniać taktowanie zegara, wydłużając czas trwania stanu niskiego, w wyniku czego szybkość transmisji urządzenia nadrzędnego będzie określana przez prędkość wolniejsze urządzenie.

ADRESOWANIE

Każde urządzenie podłączone do magistrali I2C posiada unikalny adres programowy, pod którym master adresuje je wysyłając określone polecenie. Mikroukłady tego samego typu charakteryzują się selektorem adresu, realizowanym albo w postaci wejść cyfrowych selektora, albo w postaci analogowej. Adresy są podzielone na przestrzeń adresową urządzeń podłączonych do magistrali.

Tryb normalny zakłada adresowanie siedmiobitowe. Adresowanie odbywa się w następujący sposób: po poleceniu «START» urządzenie nadrzędne wysyła pierwszy bajt, który określa, które urządzenie podrzędne jest potrzebne do komunikacji z urządzeniem nadrzędnym. Istnieje również wspólny adres wywołania, który definiuje wszystkie urządzenia na magistrali, wszystkie urządzenia (teoretycznie) odpowiadają na niego potwierdzeniem, ale w praktyce jest to rzadkie.

Tak więc pierwsze siedem bitów pierwszego bajtu to adres urządzenia podrzędnego. Najmniej znaczący bit, ósmy, wskazuje kierunek przesyłania danych. Jeśli jest „0”, wówczas informacja zostanie zapisana od urządzenia nadrzędnego do tego urządzenia podrzędnego. Jeśli «1», informacja zostanie odczytana przez mastera z tego slave'a.

Po tym, jak master zakończy wysyłanie bajtu adresu, każdy slave porównuje z nim swój adres. Każdy, kto ma ten sam adres, jest niewolnikiem i jest definiowany jako nadajnik lub odbiornik podrzędny, w zależności od wartości najmniej znaczącego bitu bajtu adresu.

Adres podrzędny może zawierać części stałe i programowalne. Dość często w jednym systemie pracuje duża ilość urządzeń tego samego typu, wówczas programowalna część adresu pozwala na zastosowanie maksymalnie urządzeń tego samego typu na magistrali. Liczba programowalnych bitów w bajcie adresu zależy od liczby wolnych pinów na chipie.

Czasami wystarczy pin z analogowym ustawieniem programowalnego zakresu adresów, np. SAA1064 - sterownik wskaźnika LED, który ma dokładnie taką realizację. Potencjał konkretnego pinu określa przesunięcie przestrzeni adresowej chipa, dzięki czemu chipy tego samego typu nie kolidują ze sobą pracując na tej samej magistrali. Wszystkie chipy obsługujące magistralę I2C zawierają zestaw adresów, które producent określa w dokumentacji.

Kombinacja «11110XX» jest zarezerwowana dla adresowania 10-bitowego. Jeśli wyobrazimy sobie wymianę danych z polecenia «START» na polecenie «STOP», będzie to wyglądać następująco:

Dozwolone są tu proste i łączone formaty wymiany danych. Połączony format oznacza, że pomiędzy „START” i „STOP” master i slave mogą działać jako odbiorniki i nadajniki, co jest przydatne na przykład w zarządzaniu pamięcią szeregową.

Niech pierwszy bajt danych prześle adres pamięci. Następnie, powtarzając polecenie «START» i odczytując adres urządzenia podrzędnego, dane z pamięci będą działać. Decyzje o automatycznym zwiększeniu lub zmniejszeniu wcześniej używanego adresu są podejmowane przez twórcę urządzenia po uprzednim przestudiowaniu dokumentacji chipa. Tak czy inaczej, po otrzymaniu polecenia START, wszystkie urządzenia muszą przywrócić logikę i przygotować się na to, że adres zostanie teraz nazwany.